PROGRAMMABLE CONTROLLERS

# #program #unit #reg byte float high float high #table indx

PLC TECOMAT Programmer's Manual

# PLC TECOMAT Programmer's Manual

# 10<sup>th</sup> edition - January 2005

#### Table of contents

| 1. INTRODUCTION                                              | 6  |

|--------------------------------------------------------------|----|

| 2. PLC AND USER PROGRAM                                      | 8  |

| 2.1. Activation sequence                                     |    |

| 2.2. PLC operating modes                                     |    |

| 2.3. User program restarts                                   |    |

| _ • • • • • F • • 9 • • • • • • • • • • •                    |    |

| 3. USER PROGRAM STRUCTURE                                    | 13 |

| 4. INSTRUCTION AND OPERAND STRUCTURE                         | 17 |

| 4.1. Immediate operand                                       |    |

| 4.1.1. Number system                                         |    |

| 4.1.2. Direct data formats                                   |    |

| 4.2. Address operand                                         |    |

| 4.2.1. Bool type operand                                     |    |

| 4.2.2. Byte / usint / sint operands                          |    |

| 4.2.3. Word / uint / int operands                            |    |

| 4.2.4. Dword / udint / dint operands                         |    |

| 4.2.5. Real type operand                                     |    |

| 4.2.6. Lreal type operand                                    |    |

| 4.3. Transition destination                                  |    |

| 4.4. Instruction parameter                                   |    |

|                                                              |    |

| 5. SCRATCHPAD MEMORY STRUCTURE                               | 34 |

| 5.1. Input images X                                          | 35 |

| 5.2. Output images Y                                         | 35 |

| 5.3. System registers S                                      | 35 |

| 5.4. User registers R                                        | 44 |

|                                                              |    |

| 6. DIRECT INPUT/OUTPUT ACCESS                                |    |

| 6.1. Direct input/output access - 16 bit model               |    |

| 6.1.1. Physical addresses in PLC TECOMAT NS950               |    |

| 6.1.2. Physical addresses in PLC TECOMAT TC400, TC500, TC600 |    |

| 6.2. Direct input/output access - 32 bit model               | 47 |

| 7. OTHER ADDRESS SPACES                                      | 10 |

| 7.1. Data D                                                  |    |

| 7.2. Tables T                                                |    |

| 7.3. DataBox additional data memory                          |    |

|                                                              |    |

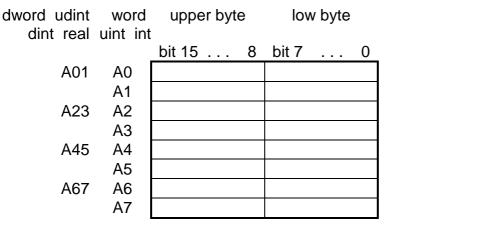

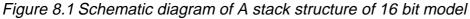

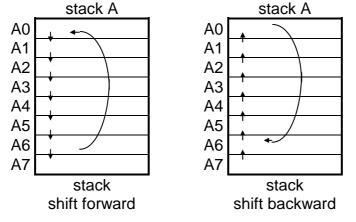

| 8. RESULT STACK                                              | 56 |

| 8.1. Stack structure                                         |    |

| 8.2. Data interpretation at the stack - 16 bit model         |    |

| 8.2.1. Data of bool type - 16 bit model                      | 58 |

|    | 8.2.2. Data of byte / usint / sint type - 16 bit model                    |      |

|----|---------------------------------------------------------------------------|------|

|    | 8.2.3. Data of word / uint / int type - 16 bit model                      |      |

|    | 8.2.4. Data of dword / udint / dint type - 16 bit model                   |      |

|    | 8.2.5. Data of real type - 16 bit model                                   | .60  |

|    | 8.3. Data interpretation at the stack - 32 bit model                      |      |

|    | 8.3.1. Data of bool type - 32 bit model                                   |      |

|    | 8.3.2. Data of byte / usint / sint type - 32 bit model                    |      |

|    | 8.3.3. Data of word / uint / int type - 32 bit model                      |      |

|    | 8.3.4. Data of dword / udint / dint type - 32 bit model                   |      |

|    | 8.3.5. Data of real type - 32 bit model                                   |      |

|    | 8.3.6. Data of Ireal type- 32 bit model                                   |      |

|    | 8.4. Switching among stacks                                               | .63  |

| 9  | COMPILER DIRECTIVES                                                       | .65  |

| ۰. | 9.1. #program                                                             |      |

|    | 9.2. #unit, #module                                                       |      |

|    | 9.3. #include, #usefile                                                   |      |

|    | 9.4. #def                                                                 |      |

|    | 9.5. #reg, #rem                                                           | .68  |

|    | 9.6. #struct                                                              |      |

|    | 9.7. #data, #table                                                        | .74  |

|    | 9.8. #if, #elif, #else, #endif                                            | .75  |

|    | 9.9. #ifdef, #ifndef, #else, #endif                                       | .76  |

|    | 9.10. #usi                                                                | .77  |

|    | 9.11. #label                                                              | .78  |

|    | 9.12. #macro, #endm                                                       |      |

|    | 9.13. #mnemo, #mnemoend                                                   |      |

|    | 9.14. #useoption                                                          | .81  |

| 10 | ). USER PROCESSES                                                         | 83   |

| 1  | 10.1. General principles of activation                                    |      |

|    | 10.2. I/O scan                                                            |      |

|    | 10.3. Restart treatment - processes P62, P63                              |      |

|    | 10.4. Loop processes                                                      |      |

|    | 10.4.1. Basic process P0                                                  |      |

|    | 10.4.2. Four-phase activated processes P1, P2, P3, P4                     |      |

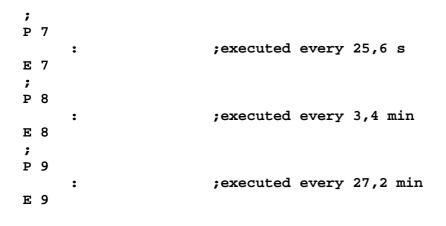

|    | 10.4.3. Time-activated processes P5, P6, P7, P8, P9                       |      |

|    | 10.4.4. User-activated processes P10 to P40                               |      |

|    | 10.4.5. P64 cycle final process                                           |      |

|    | 10.5. Interrupt processes                                                 |      |

|    | 10.5.1. Time - activated interrupt P41                                    | .93  |

|    | 10.5.2. Input - activated interrupt P42                                   |      |

|    | 10.5.3. Error - activated interrupt P43                                   | .95  |

|    | 10.5.4. HW counter - activated interrupt or incremental encoder activated |      |

|    | interrupt P44                                                             | .96  |

|    | 10.5.5. Serial channel - activated CH2 P45                                |      |

|    | 10.6. Breakpoint treatment - processes P50 to P57                         |      |

|    | 10.7. P60 Subroutine package                                              | .97  |

| 4. | I. INSTRUCTION SET                                                        | 00   |

|    |                                                                           | . 30 |

| 12. USER INSTRUCTIONS                                                      | 100 |

|----------------------------------------------------------------------------|-----|

| 12.1. Application of USI in a user program                                 |     |

| 12.2. USI for particular series of central units                           |     |

| 12.3. Creating a user-defined USI                                          | 101 |

| 12.4. C language compilers used                                            |     |

| 12.5. Example of creation of a user-defined instruction USI                | 103 |

| 12.6. Application example for USI instruction                              | 104 |

| 12.7. Comments                                                             | 104 |

|                                                                            |     |

| A. APPENDIX                                                                |     |

| A.1. Instruction execution time for central unit CPM-1E TECOMAT NS950      |     |

| A.2. Instruction execution time for central unit CPM-1M TECOMAT NS950      | 108 |

| A.3. Instruction execution time for central unit CPM-2S TECOMAT NS950      | 111 |

| A.4. Instruction execution time for central units CPM-1D TECOMAT NS950 and |     |

| TECOMAT TC400, TC500, TC600                                                | 114 |

| A.5. Instruction execution time for central units CPM-1B, CPM-2B TECOMAT   |     |

| NS950                                                                      | 119 |

| A.6. Instruction execution time for central units CP-7001, CP-7002 TECOMAT |     |

| TC700 and TECOMAT TC650                                                    | 124 |

|                                                                            |     |

# 1. INTRODUCTION

The objective of the manual is to give information on the TECOMAT programmable logic controllers (PLCs) and facilitate their programming. In the next text the central units are described by their series (see text), not by PLC types.

### Central unit (CPU) series

Every PLC TECOMAT type has several central processor units (CPUs) available that are differentiated by marking them by means of a letter representing their series.

Every series of these CPUs has given their size of memory spaces, the range of the instruction file and operand, stack structure and is the main parameter for the compiler of a user program. The following central units PLC TECOMAT are divided by their properties into the following series:

- B series NS950 CPM-1B, CPM-2B

- C series TC650, TC700 CP-7001, CP-7002

- D series TC400, TC500, TC600, NS950 CPM-1D

- E series NS950 CPM-1E

- M series NS950 CPM-1M

S series - NS950 CPM-1S, CPM-2S

#### Manual division

- The 2nd chapter describes general principles for processing a user program in a PLC.

- The 3rd chapter describes the basic structure of a user program in the Mosaic development environment.

- In 4th chapter the structure of instructions and their operands are described.

- The 5th chapter describes the structure of the scratchpad memory including a detailed overview of system services contained in system registers S.

- The 6th chapter is aimed at the basic principles of the physical addressing of the PLC units.

- The 7th chapter describes other address spaces for data D data, T tables and DataBox additional memory.

- The 8th chapter describes the structure and behaviour of result stackers

- The 9th chapter contains an overview of the directives that can be used in the Mosaic development environment including samples for their applications.

- The 10th chapter deals with user processes

- The 11th chapter contains an overview of instructions and permissible operands.

- In the 12th chapter user instructions are described

The examples in the manual are in their mnemocode only due to space. To display the examples in a relay line diagram please use the Mosaic development environment.

# **Related manuals**

Detailed information on instructions are contained in the PLC TECOMAT Instruction set manual - 16 bit model (TXV 001 05.02 - for CPU of series B, D, E, M, S) and PLC TECOMAT Instruction set manual - 32 bit model (TXV 004 01.02 - for CPU of series C).

The examples for the solution of various partial problems are contained in the PLC TECOMAT Programming examples manual – 16 bit model (TXV 001 07.02 – for CPUs of

B, D, E, M, S series) and in the PLC TECOMAT Programming examples manual – 32 bit model (TXV 004 04.02 – for CPUs of C series).

# PLC programming

The programming of control algorithms and testing of the correctness of created programs for the TECOMAT PLCs is carried out on standard PCs. For connection with the PLC standard serial channel of these PCs is used. Some types of the central units are additionally equipped with Ethernet interface and USB.

With each PLC a CD-ROM with examples and the Mosaic development environment for Windows in the Mosaic Lite version is provided.

The examples of the PLC programs contain instructions for the operation of various PLC units and also the examples from manuals TXV 001 07.02 and TXV 004 04.02.

#### The Mosaic development environment

The Mosaic development environment is a complex development tool for programming PLC TECOMAT applications and TECOREG controllers that provides a user-friendly application for program creation and debugging. It is a product running under Windows 2000 / XP platforms where a great number of modern technologies are employed. The modular structure of the Mosaic development environment enables the users to create such an environment from its parts that he will need. The following versions are available:

Mosaic Lite non-keyed version with a possibility to program a PLC with two peripheral units

Mosaic Compact enables programming compact PLC TECOMAT of series TC400, TC500, TC600 and TECOREG controllers without limitations

Mosaic Profi designated for all systems of company Teco without limitations

The basic environment contains the components necessary for creation of a program: text editor xPRO mnemocode compiler, debugger, a module for communication with the PLC, a PLC configuration module and help. A simulator of operation panels ID-07 / ID-08 and built-in TC500 panel are part of the basic environment.

The expansion of the environment is done by means of plug-ins - modules that are initialised in connection with the basic environment, so the Mosaic development environment can be expanded to have a possibility of further programming - structured text according to standard EN 61131 (Mosaic ST plugin), language of ladder diagrams (Mosaic LD plugin - under development) or function blocks (Mosaic FBD plugin - under development) and other support tools for designing operator panel screens (PanelMaker), a tool for working with PID controllers (PIDMaker), graphic on-line analysis of variables being monitored or off-line analysis of archived data (GraphMaker).

7

# 2. PLC AND USER PROGRAM

#### What is a Programmable Logic Controller

A programmable logic controller (further in the text as PLC) is a numerical control electronic system designed to control the processes in industrial environments. It uses a programmable memory for internal saving of user-oriented instructions that are used for the execution of specific functions to control various types of machines or processes through digital or analog inputs and outputs.

The company Teco a. s. manufactures PLC systems under the TECOMAT trademark.

#### Principles of user program execution

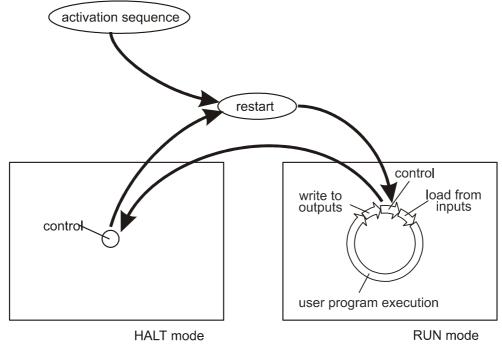

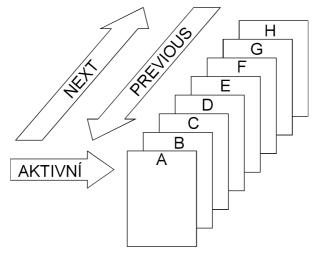

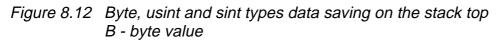

The control algorithm of a programmable logic controller is written as a sequence of instructions in the memory of a user program. The central unit stepwise reads the memory instructions, executes the operations assigned to them with the data from the scratchpad memory and stack or executes transitions in instruction sequences if the instruction is from the group of organizational instructions. When all instructions of the algorithm required are executed, the central unit updates the output variables into output peripheral units and updates the states from the input peripheral units into scratchpad memory. This is continuously repeated and the process is called a "program cycle" (figure 2.1).

#### Cyclic execution of user program

The one-time state update of input variables during the program cycle avoids the possibilities of hazardous states during solution of control algorithm (the input variables cannot be changed during computation).

Before creating a user program for the PLC it is necessary to realize this. In some cases this can facilitate the solution of the problems, sometimes it makes the situation more complicated.

Figure 2.1 Designing of a user program in PLC

On figure 2.1 a simplified layout for a user program in the PLC is shown with the following meanings:

- activation sequence is the activity of the PLC after switching the supply (see chapter 2.1.)

- restart is the activity of the PLC immediately before executing the user program (see chapter 2.3.)

- the RUN and HALT modes represent the operating modes of the PLC (see chapter 2.2.)

- read out from the inputs represents the transcription of values from the PLC input units into zone X in the scratchpad memory

- the execution of the user program is done with the values in the scratchpad memory

- write to outputs represents the transcription of values as calculated by the user program from zone Y into the PLC output units

- control includes the preparation of the PLC central unit for the solution of next program cycle

The activities into outputs, control and read out from the inputs are together called "I/O scan".

# 2.1. ACTIVATION SEQUENCE

The activation sequence represents the activity of the PLC immediately after switching power supply. It includes HW as well as SW testing of the PLC and setting the PLC to a defined initial state. In the central units equipped with setting buttons or in the PLC equipped with a keyboard panel (TC500) it is possible to call the setup mode for setting up the parameters after switching on power supply.

After the termination of the activation sequence, restart is carried out, the PLC is switched to the RUN mode and the user program is started. If the PLC diagnostics evaluates a critical error during the activation sequence, the PLC remains in the HALT mode and the error is signalised.

If the setup mode is called and the activation sequence is carried out after its termination, but the PLC then switches to the HALT mode, the user program is not executed, the PLC outputs remain locked and the PLC is expecting the commands from the superior system. The user program can be run either by means of the superior system or by switching the power supply off and on. This can be used in such cases, when there is a program in the PLC that significantly violates its basic functions. The details on behaviour of particular PLC types are given in corresponding manuals.

# 2.2. PLC OPERATING MODES

The TECOMAT PLC can run in two basic modes. The two modes are called RUN and HALT.

# **RUN Mode**

In the RUN mode, the PLC reads the values of the input signals from the input units, executes the instructions of the user program and writes the calculated values of output signals into the output units. These activities represent a program cycle.

As you can see in figure 2.1, for the PLC the inputs are evaluated discontinuously (a general property that differs digital systems from fully analog ones), the sampling

sequence of the PLC is given mainly by the size and structure of the user program. Based on the capacity of the central unit, the cycle time ranges from milliseconds up to hundreds of milliseconds.

#### HALT Mode

The HALT mode is mainly used for the activities connected with user program editing. In this mode, neither the user program nor data transmission between the central unit and peripheral units are executed.

#### PLC behaviour during a critical error

An exception from the above mentioned is, if a critical error occurs in the PLC that inhibits control activities. In this case, a mechanism for critical error treatment is started and treats the critical error from the point of control security and **always** switches the PLC to the HALT mode.

#### Operating mode change

The change of the PLC modes can be done through a superior system (master computer) that is connected to the communication channel supporting system services (serial channel, Ethernet or USB) or by means of service inputs. Typically, a standard PC represents this superior system serving as a programming means, monitoring or visualization workplace for the operation of the object being controlled.

When changing the PLC operating modes, some activities are executed standardly and some are optional.

It is possible to say in general that the change of the PLC operating mode is an activity requiring higher concentration of the operators, since in many cases it very significantly influences the state of the object being controlled. The change from the RUN to the HALT mode can be an example when the PLC stops executing of the user program and the object connected is not controlled. Therefore we recommend reading the following text very carefully.

When the change of the PLC mode is done through the Mosaic development environment, the optional activities for the mode change are part of the Project manager in folder *Environment / Control PLC*.

#### Switching from HALT to RUN

When switching from the HALT to the RUN mode the following activities are executed:

- user program integrity test

- software configuration test for the peripheral units stated in the user program

- user program start

The following items are optional:

- PLC error reset

- warm or cold restart

- output locking during user program execution

#### Switching from RUN to HALT

When switching from the RUN the HALT mode the following activities are executed:

- the of the user program stops

- locking (disconnection) of PLC outputs

The following items are optional:

- PLC error reset

- PLC output reset

If during the change from one operating mode to the other one a critical error occurs, the PLC sets the HALT mode, indicates the error and waits for clearing the error cause.

**Warning:** Control stop through the HALT mode is designated only for PLC program debugging purposes. This feature does not replace the CENTRAL STOP feature in any way. The CENTRAL STOP circuits must be connected in such a way so that their function is independent on PLC work!

Details on behaviour and possibilities of particular PLC types are given in corresponding manuals.

# 2.3. USER PROGRAM RESTARTS

Restart is an activity of the PLC, the task of which is to prepare the PLC to execute the user program. Under normal conditions restart is executed after a successful termination of the activation sequence and at every change of user program.

The TECOMAT PLCs differ two types of restart, warm and cold. The warm restart enables to holdback the values in the registers also when power supply is off (remanent zone). The cold restart always performs full memory initialisation.

# Activities during restart

During restart, the following activities are performed:

- user program integrity test

- reset of the entire PLC scratchpad

- remanent zone reset (cold restart only)

- setting of backed-up registers (warm restart only)

- initialisation of system registers S

- initialisation and check of PLC peripheral system

# User program startup without restart

The user program is also possible to be run without restarting, in this case only the user program integrity test and PLC peripheral system check are performed (not initialisation).

# User processes during restart

Dependent on the type of restart being executed functions also the scheduler of user processes P. If warm restart is executed within HALT  $\rightarrow$  RUN switching, user process P62 is executed as the first one after switching into the RUN mode (if it is programmed). In case of cold restart, user process P62 is executed as the first one. If no restart during switching into the RUN mode is executed, process P0 is executed as the first one after switching.

# Program change during PLC run

The Mosaic development environment also enables a program change when the PLC is running. In this case it is important to realize that for the period of loading of a new

program, the execution of the program is topped without locking the outputs. This can also take a couple of seconds!

#### Restart type preset

The type of restart after starting a user program from the Mosaic development environment can be set in the Manager project in folder *Environment | Control PLC*. For the type of restart after switching the power supply on for the PLC (after a successful activation sequence) is given the option in folder Sw / Cpm.

This setting will automatically be transferred during compilation into the user program by means of directive *#useoption*.

# 3. USER PROGRAM STRUCTURE

#### Programming language of xPRO compiler

The programming language of the xPRO compiler within the Mosaic development environment is based on the mnemonic language of the PLC as described in chapter 4. The extension is given by a possibility to use symbolic names of the variables (registers, labels, etc.) and directives for the compiler. The xPRO compiler can be incorporated with compilers of higher language, e.g. according to IEC 61131-3.

#### Rules for program write

The user program write is governed by several simple rules:

- Each line of the source text of the program can have one instruction at most. This means the line can also be empty or can contain just a comment. Attention a label is also an instruction!

- Symbolic names can begin with letters 'a' to 'z', 'A' to 'Z' or '\_', and can also contain characters 'a' to 'ž', 'A' to 'Ž', '0' to '9' and '\_' (underline character). A symbolic name must not begin neither with a digit nor a character with a diacritical mark (wedges and acute accents).

Attention! A symbolic name must not be identical with any of the reserved symbols of the compiler (see Table 3.1).

- Comments start after the semi-colon character ';'. The entire text beyond this character is considered as a comment and ignored.

- Lower-case and upper-case letters can be used arbitrarily, the compiler internally converts all letters to upper-case ones, thus it is not case sensitive.

When using these rules it is possible to write the following simple program:

#### Example 3.1

| #def<br>#def<br>#def | Start<br>Outpu<br>Value | ıt –  | %X0.0<br>%Y0.0<br>21 | declaration of inputs, outputs and constants; |

|----------------------|-------------------------|-------|----------------------|-----------------------------------------------|

| #reg                 | bool                    | Reset | :                    | ;declaration of registers                     |

| #reg                 | uint                    | Timer | , Counter            |                                               |

| ;                    |                         |       |                      |                                               |

| Р 0                  |                         |       |                      | ;program start                                |

|                      | LD                      | Start | Stop                 | ;timer control bit                            |

|                      | LD                      | Reset | :                    | ;setting timer to zero                        |

|                      | LD                      | Value | 2                    | ;timer preset                                 |

|                      | RTO                     | Timer | .3                   | ;second timer function                        |

|                      | WR                      | Outpu | ıt                   | ;output                                       |

|                      | JMC                     | Jump  |                      | ;conditional jump                             |

|                      | INR                     | Count | er                   | ;number of cycles, when Output is = 0         |

| Jump:                |                         |       |                      | ;label                                        |

| Е 0                  |                         |       |                      | ;program end                                  |

The program as per example 3.1 represents the basic components of the user program in the Mosaic development environment.

The Mosaic development environment automatically creates the program header in the control file *xxx.mak*, where xxx is the name of the project within the project group. In the

Mosaic development environment the *#program* directive is not written into the source file, as opposed to the xPRO environment where the directive is used.

After the program header is created, declarations of inputs, outputs, constants and registers follow. If we do not use these declarations, the user program then can be written by means of absolute operands (i.e. X, Y, S, D, R registers). But we do not recommend fundamentally to do this since this way is very confused and makes prospective program modifications very difficult. In addition, some program designs using structures and symbolic references are almost impracticable when using absolute addresses.

Problems also can occur when transferring the program algorithm in absolute representation among particular types of central units.

The central units with the 32 bit stack width supporting a higher language require so called percent convention when writing absolute operands, this is to say that the % character has to be written before an absolute operand character (see example 3.1). All prefixes (*indx*, *bitpart*, *bitcnt*, *offset*, *sizeof*) are written with two underline characters (*\_\_indx*, *\_\_bitpart*, *\_\_bitcnt*, *\_\_offset*, *\_\_sizeof*) and the following object is parenthesised. These measures are necessary to eliminate collision with the symbolic names of a higher language. In case of the central units with the 16 bit stack width, the use of the percent character and underline characters before an absolute operand is not obligatory, but we recommend to use them due to code transferability.

Software configuration is the description of the peripheral units used by means of the *#unit* directive, or *#module* (TC650, TC700) respectively. These directive determine the interconnection of the inputs and outputs with the scratchpad memory and enable the data transfer between the user program and environment. The Mosaic development environment generates a list of the *#unit / #module* directives, related initialisation tables and necessary declarations automatically based on filled-in tables in the configuration section (Project manager, folder *Hw | HW Configuration*) in an individual file *xxx.hwc*, where xxx is the name of the project.

If we check the option *Suppress directive #UNIT* in the configuration section, then the PLC will execute the user program only in the scratchpad memory. The inputs will not be downloaded into the scratchpad memory and there will be no write into the outputs in the scratchpad memory. The outputs will remain locked. This state can be useful when debugging an algorithm in the PLC without connected technology.

After this the user program follows. Since the Mosaic development environment contains the xPRO compiler, the user program instruction write in this environment is identical to the recent xPRO development environment. Each user program must have the P0 process even if it should remain empty. The P0 and E0 instructions are obligatory ones.

Using comments is not obligatory, but the rule is, the better the program is commented with more details, the easier to do some modifications later on is.

The indentation of the instruction by means of tabulators, as you can see from the example, is not necessary, it is enough to use the space character to separate the operand and all instructions could be written from the line margin but we try to do our best to have the program as well-ordered as possible.

In table 3.1 there is a list of reserved compiler symbols that cannot be used as symbolic names since they are used by the compiler to mark preset object. It is necessary to pay attention to this list since the mistakes caused by using the reserved symbols for another purpose could result in an unpredictable behaviour.

| (valid for upper-case and lower-case letters) |              |                 |           |                 |            |

|-----------------------------------------------|--------------|-----------------|-----------|-----------------|------------|

| A*                                            | CHGS         | DIGITOUT8       | FTSS      | LDQ             | OPTION     |

| ABS                                           | CHPAR        | DIGIT_050       | G*        | LDS             | OR         |

| ABSD                                          | CMDF         | DIGIT_200       | GS*       | LDSR            | ORC        |

| ABSL                                          | CMF          | DIGIT_300       | GT        | LDU             | ORL        |

| ACS                                           | CML          | DIGIT_400       | GTDF      | LDX             | P          |

| ACSD                                          | CMP          | DIGIT_500       | GTF       | LDY             | PERIOD_500 |

| ADD                                           | CMPS         | DIGIT_600       | GTS       | LEA             | PERIOD_600 |

| ADD                                           | CNT          |                 | H*        | LEAX            | PID        |

|                                               |              | DIGIT_633       |           |                 |            |

| ADF                                           | CNV          | DIGIT_63X       | HIGH      | LEAY            | PIDA       |

| ADL                                           | COLD         | DIGOUT16        | HPD       | LET             | PLC        |

| ADX                                           | COS          | DIGOUT8         | HPE       | LETX            | POP        |

| ALIGNED                                       | COSD         | DIG_10IN_10OUT  | HS*       | LINK            | POPB       |

| ANALOG_050                                    | COUNT_500    | DIG_5IN_6OUT    | HYP       | LINT            | POPL       |

| ANALOG_200                                    | COUNT_600    | DINT            | HYPD      | LMS             | POPQ       |

| ANALOG_300                                    | CP7001       | DISPASCII       | IC_04     | LN              | POPW       |

| ANALOG_400                                    | CP7002       | DISPHEX         | IDB       | LND             | POW        |

| ANALOG 500                                    | CPM1A        | DIV             | IDFL      | LOG             | POWD       |

| ANALOG_600                                    | CPM1B        | DIVL            | IDFW      | LOGD            | PROGRAM    |

| ANC                                           | CPM2B        | DIVS            | IF        | LONG            | PRV        |

| AND                                           | CPM1D        | DL0, DL1*       | IFDEF     | LOW             | PSHB       |

| ANL                                           | CPM1E        | DQ0, DQ1*       | IFL       | LREAL           | PSHL       |

| AN 4IN                                        | CPM1M        | DG0, DG1<br>DS* | IFNDEF    | LT              | PSHQ       |

| AN_4IN_4OUT                                   | CPM1S        | DST             | IFW       | LTB             | PSHW       |

| AN_4IN_4001<br>AN_8IN                         | CPM2S        | DT              | ILDF      | LTDF            | PUBLIC     |

| AN_8IN_4OUT                                   | CPM25<br>CS* | DW0, DW1*       | ILDF      | LTF             | PUT        |

|                                               |              |                 |           |                 |            |

| AS*                                           | CSG          | DWORD           |           | LTS             | PUTX       |

| ASB                                           | CSGD         | E               | INCLUDE   | LWORD           | R*         |

| ASN                                           | CSGL         | EC              | INDX**    | M*              | R0, R1*    |

| ASND                                          | CTD          | ED              | INR       | M0, M1*         | RCHK       |

| ATN                                           | CTU          | EOC             | INT       | MACRO           | RD0, RD1*  |

| ATND                                          | D*           | EQ              | INTIN_500 | MAX             | RDB        |

| B*                                            | D0, D1*      | EQDF            | INTIN_600 | MAXD            | RDT        |

| BAS                                           | DATA         | EQF             | IRC_500   | MAXF            | REAL       |

| BCD                                           | DATE         | ENDIF           | IRC_600   | MAXS            | REC        |

| BCL                                           | DCR          | ENDM            | IWDF      | MD0, MD1*       | RED        |

| BCMP                                          | DD0, DD1*    | ES*             | IWF       | MF0, MF1*       | REG        |

| BET                                           | DEF          | ETH1, ETH2      | JB        | MIN             | REI        |

| BETX                                          | DF0, DF1*    | EXP             | JC        | MIND            | RES        |

| BIL                                           | DFF          | EXPD            | JMC       | MINF            | RESM       |

| BIN                                           | DFST         | EXTB            | JMD       | MINS            | RESX       |

| BIT                                           | DID          | EXTW            | JMI       | ML0, ML1*       | RET        |

| BITCNT**                                      | DIDF         | F*              | JMP       | MNT             | RF0, RF1*  |

| BITPART**                                     | DIF          | r<br>FDF        | JNB       | MOD             | RFRM       |

| BOOL                                          | DIFCNT100MS  | FIL             | JNC       | MODS            | RL0, RL1*  |

| BOX                                           | DIG2         | FIS             | JNS       | MOV             | RND        |

| BP                                            | DIG4         | FIT             | JNZ       | MQ0, MQ1*       | RNDD       |

| BRC                                           | DIG8         | FLG             | JS        | MQ0, MQ1<br>MTN | ROL        |

|                                               |              |                 | JZ        | MUD             |            |

| BRD                                           | DIGIN16      | FLO             |           |                 | ROR        |

| BRE                                           | DIGIN8       | FLOAT           |           | MUDF            | RQ0, RQ1*  |

| BS*                                           | DIGIN8OUT8   | FLOD            | L0, L1*   | MUF             | RTO        |

| BYTE                                          | DIGIT2       | FNS             | LABEL     | MUL             | RW0, RW1*  |

| C*                                            | DIGIT4       | FNT             | LAC       | MULS            | S*         |

| CAC                                           | DIGIT8       | FS*             | LD        | MW0, MW1*       | S0, S1*    |

| CAD                                           | DIGITIN16    | FST             | LDC       | NEG             | SCH2       |

| CAI                                           | DIGITIN32    | FTB             | LDI       | NGL             | SCMP       |

| CAL                                           | DIGITIN64    | FTBN            | LDIB      | NOP             | SCNV       |

| CEI                                           | DIGITIN8     | FTM             | LDIL      | NXT             | SCON       |

| CEID                                          | DIGITOUT16   | FTMN            | LDIQ      | OFF             | SD0, SD1*  |

| CH1, CH2                                      | DIGITOUT32   | FTS             | LDIW      | OFFSET**        | SDEL       |

| CHG                                           | DIGITOUT64   | FTSF            | LDL       | ON              | SEQ        |

| -                                             |              |                 |           |                 |            |

Table 3.1 List of reserved compiler symbols that cannot be used as a symbolic name (valid for upper-case and lower-case letters)

| (valid for upper-case and lower-case letters) - continued |           |           |            |           |               |

|-----------------------------------------------------------|-----------|-----------|------------|-----------|---------------|

| SET                                                       | STATM     | TER       | UNLK       | WRX       | _ANALOG_      |

| SETX                                                      | STDF      | TF0, TF1* | USB1, USB2 | WRY       | _CHX          |

| SF0, SF1*                                                 | STE       | TIME      | USEOPTION  | WSTRING   | _GT_40_       |

| SFL                                                       | STF       | TL0, TL1* | USI        | WTB       | _GT_40A_      |

| SFND                                                      | STK       | TOD       | USINT      | Х*        | _IC_12_       |

| SFR                                                       | STRING    | TOF       | UWDF       | X0, X1*   | _IC_13_       |

| SHL                                                       | STRUCT    | TON       | UWF        | XD0, XD1* | _IM_61_       |

| SHR                                                       | SUB       | TQ0, TQ1* | UW0,UW1    | XF0, XF1* | _INTELIG      |

| SIN                                                       | SUDF      | TR050     | UX_52      | XH_04     | _INTELIGENT   |

| SIND                                                      | SUF       | TR200     | VIRTMUX    | XL0, XL1* | _IR_11_       |

| SINS                                                      | SUL       | TR300     | WAC        | XOC       | _IT_04_       |

| SINT                                                      | SUX       | TW0, TW1* | WARM       | XOL       | _IT_06_       |

| SIZEOF**                                                  | SW0, SW1* | U*        | WDB        | XOR       | _IT_12_       |

| SL0, SL1*                                                 | SWL       | U0, U1*   | WMS        | XQ0, XQ1* | _IT_15_       |

| SLEN                                                      | SWP       | UD0, UD1* | WORD       | XW0, XW1* | _KEYDISP_200_ |

| SLFT                                                      | SYNC      | UDFL      | WR         | X_OFF     | _KEYDISP_500_ |

| SMID                                                      | SYS       | UDFW      | WRA        | X_ON      | _OT_04_       |

| SND                                                       | T*        | UDINT     | WRC        | Y*        | _OT_04X_      |

| SPEC                                                      | T0, T1*   | UF0, UF1* | WRI        | Y_OFF     | _OT_05        |

| SPECIAL                                                   | TABLE     | UFL       | WRIB       | Y_ON      | _OT_05X       |

| SQ0, SQ1*                                                 | TAN       | UFW       | WRIL       | Y0, Y1*   | _PLCTYPE_     |

| SQR                                                       | TAND      | UINT      | WRIQ       | YD0, YD1* | _SC_11_       |

| SQRD                                                      | TC400     | UL0, UL1* | WRIW       | YF0, YF1* | _SPECIALTAB_  |

| SRC                                                       | TC500     | ULDF      | WRS        | YL0, YL1* | _SPECTAB_     |

| SRD                                                       | TC600     | ULF       | WRSR       | YQ0, YQ1* |               |

| SREP                                                      | TC700     | ULINT     | WRT        | YW0, YW1* |               |

| SRGT                                                      | TD0, TD1* | UNIT      | WRU        | _ANAL_    |               |

Table 3.1 List of reserved compiler symbols that cannot be used as a symbolic name (valid for upper-case and lower-case letters) - continued

<sup>\*</sup> Symbols marked \* are in the 32 bit stack width central units obligatorily used with the % character and then it is possible to use them as a symbolic name. For example:

| %SW12         | ;absolute marking of register SW12 |

|---------------|------------------------------------|

| #def SW12 %X0 | ;symbolic marking of input         |

\*\* Symbols marked \*\* are in the 32 bit stack width central units obligatorily used with the \_\_\_\_\_ characters and then it is possible to use them as a symbolic name. For example:

| indx (item)  | ;use of prefixindx            |

|--------------|-------------------------------|

| #def indx 20 | ;symbolic marking of constant |

Note: Due to continuous development and enhancement of the xPRO compiler we do not recommend using one to four-letter symbolic names (mainly originating from English names or abbreviations) separately or in combination with a numeric index. When really necessary to use such a name we recommend using the underline character before it (\_A as an example).

# 4. INSTRUCTION AND OPERAND STRUCTURE

#### Instruction

An instruction is the smallest element of the user program. It consists of a mnemocode and an operand. Formally, we distinguish between operand-free instructions from instructions with one operand.

#### **Mnemonic code**

A mnemocode is a group of one or three letters having a meaning of an abbreviation usually derived from the English name of the instructions (for example AND, OR, XOR, NEG, FLG, RET, ED, EC).

#### **Operand-free instruction**

The operand-free instruction usually processes the content of the stack top, or also other stack layers of the stack pertinently or executes an unequivocally specified activity (for example return from subroutine). The operand-free instruction consists of the mnemocode only and its activity is not necessary to specify in more detail.

#### Instruction with one operand

The mnemocode of the operand instruction is followed with a group of characters that specify one of the operands as agreed and with this operand the instruction works or which specify the behaviour of the instruction (for example instruction parameter, number of repetitions of the basic operation, jump position, etc.). The second operand for logical and arithmetic operations is the stack top. The operand is separated from the mnemocode at least by one space character.

Absolute addresses are written beginning with the % character, which is not obligatory when programming 16 bit stack width central units, but we recommend to use them with regard to the transferability of the user programs to the central units with the 32 bit stack width.

The operands instructions can have the following structure, for example:

AND %X0 AND %Y2 OR %RW4 %RW16.1 TON JMP %L15 Ρ 0 NOP 17 LTB %T5 POP 3 LD123 %10110110 T.D

#### Sort of operands

According to the meaning we can specify four types of operands:

immediate operand - the instruction operand is directly a numeric value (written in the numeric system selected), with which the required instruction is executed

address operand - determines the address of the position, from where the operation result is read or where it is saved transition destination - the operand is the number of the label (a labelled position in the program), where the programmed transition (a jump or a call) is directed

instruction parameter - a single numeric or letter parameter marking the instruction in question (for example process number, label number, null instruction number, stack) or specifies its behaviour (for example number of stack shifts).

From the format point of view there are no other instructions. If some instructions or the subroutine require more parameters (function blocks, table or block instructions), they are passed in several stack levels where the sequences of instructions LD or LDC are saved.

#### **Operand types**

According to data width several operand types are distinguished. These types are marked in two ways - one way is marked as TECOMAT which is the marking used with previous compiler versions, the second way of marking corresponds to IEC 61131. Both ways of identification can be normally used. An overview is given in Table 4.1.

| TECOMAT | IEC 61131 | Width   | Numeric range                                                   |

|---------|-----------|---------|-----------------------------------------------------------------|

| bit     | bool      | 1 bit   | Boolean information 0 - 1                                       |

|         | byte      | 8 bits  | 0 to 255                                                        |

| byte    | usint     | 8 bits  | 0 to 255                                                        |

|         | sint      | 8 bits  | -128 to +127                                                    |

|         | word      | 16 bits | 0 to 65 535                                                     |

| word    | uint      | 16 bits | 0 to 65 535                                                     |

|         | int       | 16 bits | -32 768 to +32 767                                              |

|         | dword     | 32 bits | 0 to 4 294 967 295                                              |

| long    | udint     | 32 bits | 0 to 4 294 967 295                                              |

|         | dint      | 32 bits | -2 147 483 648 to +2 147 483 647                                |

| float   | real      | 32 bits | $\pm 1,175494 \times 10^{-38}$ to $\pm 3,402823 \times 10^{38}$ |

| double  | Ireal     | 64 bits | $\pm 2,2 \times 10^{-308}$ to $\pm 1,8 \times 10^{308}$         |

Tab.4.1 Operand types

Types float and double, or real and Ireal as the case may be contain numeric formats with floating point according to IEEE-754.

In the following text we will be using the types according to IEC 61131. The information is valid also for equivalent types of TECOMAT.

#### 4.1. IMMEDIATE OPERAND

In this case a number is written as the operand of the instruction that is directly processed by the instruction - data carried directly in the instruction. The immediate operand thus has the meaning of a numeric constant.

#### 4.1.1. Number systems

#### Constant entry in common number systems

The numeric constant can be entered in any numeric system in the following form:

#n#cccc

where n stands for the base of the numeric system,

cccc is the number itself in the numeric system selected

If the base of the numeric system is greater than 10, then the particular digits can be written decimally (in the form of a two-digit number) and are separated with a dot.

LD #8#360 ;octal number system WR #60#15.28.35 ;write time data in hours, ;minutes and seconds by means of ;sexagesimal system

#### Shortened entry in most frequently used number systems

The most frequently numeric systems used are the decimal systems used mainly for arithmetic instructions, the binary and hexadecimal systems used preferably for logic instructions. These systems allow a shortened notation.

If the number is written without specifying a numeric system to be used it is considered to be a decimal number. The binary system is marked with the % character before the number. The hexadecimal system is marked with the \$ character before the number where digits 0 to 9, A to F are used:

| LD  | 152               | ;decimal system     |

|-----|-------------------|---------------------|

| AND | %0111110100110100 | ;binary system      |

| AND | \$7D34            | ;hexadecimal system |

#### **Negative numbers**

For the decimal system the write of a negative number is permissible. The negative sign causes that instead of the binary equivalent of the number the binary complement is saved as the instruction operand of this 8 bit number (sint), 16 bits (int) or 32 bits (dint)(according to the type of instruction).

For example, the value of -1 will have the value of 255 in the sint format, the value of 65 535 in the int format and the value of 4 294 967 295 in the dint format. The real and Ireal format already contains the information on the sign.

#### 4.1.2. Immediate data formats

The format of the numeric constant is unequivocally determined by the type of instruction. The instructions expect the constants of type corresponding to the description of appropriate instruction.

If to the instruction requiring a numeric constant of 32 bit width a number of 8 bit width is written, then the compiler adds zeros to that number to 32 bit width. This way is thus permissible.

| LDL | \$1F             | ;32 bit width expected |

|-----|------------------|------------------------|

| LDL | \$000001F        | ; identical notation   |

| AND | 811              | ;16 bit width expected |

| AND | %000000000000011 | ;identical notation    |

The numeric constant of the real and Ireal types is permissible only for the decimal system. Since the real type has the same length as the dword, udint and dint types but entirely different data interpretation, the numeric constant entry of the real type marks out that it contains the decimal point even if it is an integral number. The presence of the decimal point is thus the information important for the xPRO compiler to compile this constant into the correct format.

#### LDL 1

| LDL | 1.0 | ;type real  |

|-----|-----|-------------|

| LDQ | 1.0 | ;type lreal |

Note: Instead of the LDL instruction, the LD instruction is used in the user programs for the central units with the stack width of 32 bits (CPU series C). Nevertheless, the compiler accepts also the LDL instruction and converts it automatically to the LD one. By doing this, program portability is ensured (see chapter 8 Result stack).

Table 4.2 Immediate operand ranges

| byte / sint   | byte / usint      | V                | vord / int                                 | word / uint             |  |

|---------------|-------------------|------------------|--------------------------------------------|-------------------------|--|

| -128 to +127  | 0 to 255          | -327             | 68 to +32 767                              | 0 to 65535              |  |

|               | %0 to %11111111   |                  |                                            | %0 to %1111111111111111 |  |

| -\$80 to \$7F | \$0 to \$FF       | -\$80            | 000 to \$FFFF                              | \$0 to \$FFFF           |  |

|               | #60#0 to #60#8.15 |                  |                                            | #60#0 to #60#18.12.15   |  |

| dword / dint  |                   |                  | lo                                         | ong / udint             |  |

| -214748364    | 48 to +2147483647 | 0 to 4294967295  |                                            |                         |  |

|               |                   | %0 to            | %0 to %11111111111111111111111111111111111 |                         |  |

| -\$800000     | 00 to \$FFFFFFFF  | \$0 to \$FFFFFFF |                                            |                         |  |

|               |                   |                  | #60#0 t                                    |                         |  |

|               |                   |                  | #00#0 [                                    | o #60#59.59.59 *        |  |

|               | real              |                  | #00#0 (                                    | lreal                   |  |

\* Sexagesimal system is valid for hours, minutes and seconds, not for days.

#### Symbolic name used as operand

As a immediate operand it is also possible to use a symbolic name defined by the *#def* directive. A mathematical expression can be used, too.

| #def | numbe | r 10      |     |    |

|------|-------|-----------|-----|----|

|      | LD    | number    | ;LD | 10 |

|      | LD    | number *4 | ;LD | 40 |

#### Object number as operand – prefix \_\_indx, \_\_bitpart, \_\_bitcnt

If we need to use a register number, table number or label number as an operand, then the \_\_\_\_indx prefix will be used.

| #reg | uint | register1, register2 | ;RW0,RW2 |

|------|------|----------------------|----------|

|      | LD   | indx (register1)     | ;LD 0    |

|      | LD   | indx (register2)     | ;LD 2    |

If we need to use a register bit number as an operand, then the <u>bitpart</u> prefix will be used.

#reg bool register1,register2 ;R10.0,R10.1

LD \_\_bitpart (register1);LD 0

LD \_\_bitpart (register2);LD 1

If we need to use the bit ordinal number as an operand within the entire register zone, then the \_\_\_bitcnt will be used.

#reg bool register1,register2 ;R10.0,R10.1

LD \_\_bitcnt register1 ;LD 80

LD \_\_bitcnt register2 ;LD 81

#### Object address as operand - prefix \_\_offset

By means of prefix *\_\_\_\_offset* we can work with an object address as it is required by some special functions as the pointer for data positioning.

#reg usint work[20] ;R150

LD \_\_offset (list) ;LD 790 - for CPUs of B, D, E, M, S series

;LD 24726 - for CPU of C series

#### Length of object as operand - prefix \_\_sizeof

By means of the \_\_\_\_\_\_size of prefix we can work with the object length, mostly a structure.

#struct list usint first, uint second, real third

LD \_\_\_\_\_sizeof (list) ;LD 7

#### 4.2. ADDRESS OPERAND

#### Address operand space type

The address operand has the meaning of the position address, from where the information being processed is read or where the operation result is saved. The type of operand space is marked with the first character in the operand:

- X scratchpad input image

- Y scratchpad output image

- S scratchpad system registers

- R scratchpad user registers

- U physical addresses

- D user program data constant zone

- T user program table zone

This first character is sometimes called as "operand space specifier".

In the user programs for the central units with the 32 bit stack width it is obligatory to use the beginning character of % before the specifier. By this it is determined unequivocally that this is an absolute address and not a symbolic name. With the central units with 16 bit stack width this way of notation is not obligatory, but we recommend to use it with regard to user program transferability.

#### Symbolic name used as operand

Usually, we use the symbolic name assigned by means of the *#def*, *#reg*, *#rem*, *#data* or *#table* directives as the address operand.

```

#def input %X0

#rem bool register1 ;R0.0 remanent

#reg bool register2 ;R1.0

#data usint record = 1,2,3,4 ;D0, D1, D2, D3

#table uint 10,tab = 1,2,3,4 ;TW10

```

| bool            | byte / usint / sint | word / uint / int     |  |  |  |

|-----------------|---------------------|-----------------------|--|--|--|

| X0.0 - X15.7    | X0 - X15            | XW0 - XW14            |  |  |  |

| Y0.0 - Y15.7    | Y0 - Y15            | YW0 - YW14            |  |  |  |

| S0.0 - S63.7    | S0 - S63            | SW0 - SW62            |  |  |  |

| R0.0 - R255.7   | R0 - R255           | RW0 - RW254           |  |  |  |

| -               | U\$0000 - U\$FFFF * | UW\$0000 - UW\$FFFE * |  |  |  |

| D0.0 - D255.7   | D0 - D255           | DW0 - DW254           |  |  |  |

| T0.0 - T255.0 * | T0 - T255 *         | TW0 - TW255 *         |  |  |  |

| Table 40   |                        | n ana al na ana a ƙan a arisa 🗖 ana I M |

|------------|------------------------|-----------------------------------------|

| I able 4.3 | Central unit address o | perand ranges for series E and M        |

Not implemented in central units of series E.

Table 4.4 Central unit address operand ranges for series S

| bool          | byte / usint / sint | word / uint / int   |

|---------------|---------------------|---------------------|

| X0.0 - X127.7 | X0 - X127           | XW0 - XW126         |

| Y0.0 - Y127.7 | Y0 - Y127           | YW0 - YW126         |

| S0.0 - S63.7  | S0 - S63            | SW0 - SW62          |

| R0.0 - R511.7 | R0 - R511           | RW0 - RW510         |

| -             | U\$0000 - U\$FFFF   | UW\$0000 - UW\$FFFE |

| D0.0 - D255.7 | D0 - D255           | DW0 - DW254         |

| T0.0 - T255.0 | T0 - T255           | TW0 - TW255         |

Table 4.5 Central unit address operand ranges for series B and D

| bool           | byte / usint / sint | word / uint / int   |

|----------------|---------------------|---------------------|

| X0.0 - X127.7  | X0 - X127           | XW0 - XW126         |

| Y0.0 - Y127.7  | Y0 - Y127           | YW0 - YW126         |

| S0.0 - S63.7   | S0 - S63            | SW0 - SW62          |

| R0.0 - R8191.7 | R0 - R8191          | RW0 - RW8190        |

| -              | U\$0000 - U\$FFFF   | UW\$0000 - UW\$FFFE |

| D0.0 - D255.0  | D0 - D255           | DW0 - DW254         |

| T0.0 - Tmax    | T0 - T255           | TW0 - TW255         |

| dword / udint / dint | real         |

|----------------------|--------------|

| XL0 - XL124          | XF0 - XF124  |

| YL0 - YL124          | YF0 - YF124  |

| SL0 - SL60           | SF0 - SF60   |

| RL0 - RL8188         | RF0 - RF8188 |

| -                    | -            |

| DL0 - DL252          | DF0 - DF252  |

| -                    | -            |

Table 4.6 Central unit address operand ranges for series C

| bool            | byte / usint / sint | word / uint / int |

|-----------------|---------------------|-------------------|

| X0.0 - X8191.7  | X0 - X8191          | XW0 - XW8190      |

| Y0.0 - Y8191.7  | Y0 - Y8191          | YW0 - YW8190      |

| S0.0 - S6143.7  | S0 - S6143          | SW0 - SW6142      |

| R0.0 - R40955.7 | R0 - R40955         | RW0 - RW40954     |

| D0.0 - D2047.7  | D0 - D2047          | DW0 - DW2046      |

| T0.0 - Tmax.0   | T0 - Tmax           | TW0 - TWmax       |

| dword / udint / dint | real          | Ireal         |

|----------------------|---------------|---------------|

| XL0 - XL8188         | XF0 - XF8188  | XD0 - XD8184  |

| YL0 - YL8188         | YF0 - YF8188  | YD0 - YD8184  |

| SL0 - SL6140         | SF0 - SF6140  | SD0 - SD6136  |

| RL0 - RL40952        | RF0 - RF40952 | RD0 - RF40948 |

| DL0 - DL2044         | DF0 - DF2044  | DD0 - DD2040  |

| TL0 - TLmax          | TF0 - TFmax   | -             |

\* In the central units of series C the U-operands are replaced with the RFRM system instructions which performs immediate update of dedicated peripheral module data.

Note: Apart from the data, each T-table additionally occupies 4 bytes for service information in the memory.

A list of T-table addresses created by the compiler is part of the user program. This list has n+1 items, where n stands for the highest table number declared in the user program. In the list, addresses of all tables from T0 to Tn are listed including those not being declared (having zero address). As the result of this, if we use only the tables with high numbers in the user program, the table address will occupy unnecessarily a great part of the memory determined for the user program.

Therefore, we recommend to number the tables ascendingly from 0 (the xPRO compiler supports this principle when using symbolic names of the tables).

# 4.2.1. Bool type operand

Data of the bool type in the scratchpad represents one concrete bit in the byte given by the address of the byte and the number of the bit.

Data assumes values 0 and 1 (due to a different interpretation on the stack we call them log.0 and log.1).

|    |   |   |   |   | .3 |   |   |   |

|----|---|---|---|---|----|---|---|---|

| R0 | х | Х | х | b | х  | Х | х | Х |

Figure 4.1 Bool type data saving in the scratchpad b - logical value of the bit (log.0 or log.1)

The bool type operand is addressed by the byte address in the operand space and the bit number inside this byte. In absolute expression, the byte address is unequivocally given by the number in the address operand. The bit number has a value 0 to 7 and is entered after the point, for example:

| LD | %X1.2   |

|----|---------|

| WR | %Y1.7   |

| LD | %S53.4  |

| WR | %R123.6 |

| LD | %D25.6  |

|    |         |

The lowest (low) bit of the byte correspond to 0, the highest (upper) bit of the byte corresponds to 7. If the contents of the byte is displayed as a binary number or as a sequence of bit values on the line, then the lowest bit is rightmost and the top one leftmost.

The U-operands do not enable bit access.

The T-operands determining the bit access to the tables always have the bit number equal to 0. So the bit access is distinguished from the byte one, otherwise the bit number does not have any meaning in this case.

LTB %T4.0;load item from bit table T4 (the item number ; is determined by the index saved on the stack top)

#### Symbolic expression

In symbolic expression the operand is determined by the *#def*, *#reg*, *#rem*, *#data* and *#table* directives.

```

#def input %X2.1

#rem bool register1 ;R0.0 remanent

#reg bool register2 ;R1.0

#reg bool register3 ;R1.1

#data bool record = 1,0,1,0 ;D0.0, D0.1, D0.2, D0.3

#table bool tab = 1,0,1,1 ;T0.0

```

#### Casting to bool

If we need to cast an operand locally in our user program (we need to use another operand type than it is defined by the above mentioned directives) it is possible to cast it locally to the bool type by adding the bit number. The bits can be numbered within the entire operand width, thus from 0 to 7 for 8 bit width, 0 to 15 for 16 bit width and 0 to 31 for 32 bit width.

| #reg   | usint | registerl        | ;R0  |       |

|--------|-------|------------------|------|-------|

| #reg   | uint  | register2        | ;RW1 |       |

| #reg   | udint | register3        | ;RL3 |       |

| #table | usint | tab = 1, 2, 3, 4 | ;T0  |       |

| ;      |       |                  |      |       |

| I      | D re  | egister1.0       | ;LD  | %R0.0 |

| I      | D re  | egister2.5       | ;LD  | %R1.5 |

| I      | D re  | egister3.31      | ;LD  | %R6.7 |

| I      | TB ta | ab.0             | ;LTB | %T0.0 |

|        |       |                  |      |       |

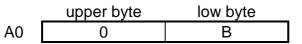

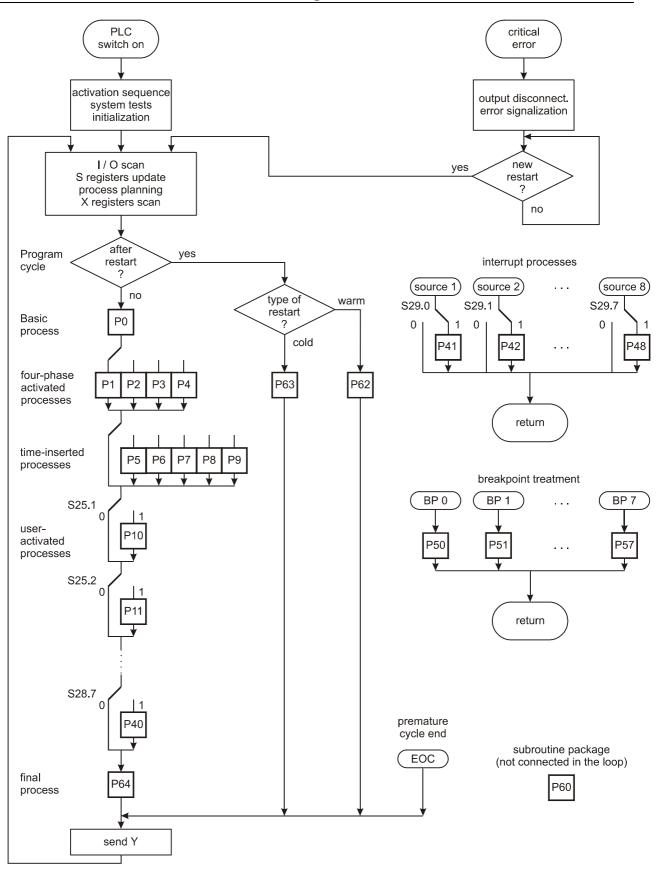

#### 4.2.2. Byte / usint / sint operand

The byte, usint and sint types data in the scratchpad represent one concrete byte given by the address.

The data assumes values of 0 to 255 (byte, usint) or, when using the highest (upper) bit as the sign, -128 to +127 (sint).

Figure 4.2 Byte, usint, sint data saving in the scratchpad *B* - byte value

In absolute expression the operand is addressed by the number in the address operand.

LD %X1 WR %Y0 LD %S53 WR %R123 LD %D25

#### LTB %T4

The U-operand is addressed by the physical hexadecimal address of 16 bit width (\$ stands for the hexadecimal number system).

LD %U\$9101 ;address hexadecimal value

#### Symbolic expression

In symbolic expression the operand is determined by the *#def*, *#reg*, *#rem*, *#data* and *#table* directives.

| #def ir | nput %X | 2                   |                 |

|---------|---------|---------------------|-----------------|

| #rem    | usint   | register1           | ;R0 remanent    |

| #reg    | byte    | register2           | ;R1             |

| #reg    | usint   | registr3            | ;R2             |

| #reg    | sint    | registr4            | ;R3             |

| #data   | usint   | record = 1, 2, 3, 4 | ;D0, D1, D2, D3 |

| #table  | usint   | tab = 1, 2, 3, 4    | <b>;</b> T0     |

#### Casting to byte, usint, sint

If we need to cast an operand locally in our user program (we need to use another operand type than it is defined by the above mentioned directives) it is possible to cast it locally by adding the *byte, usint, sint* prefixes.

| #reg   | bool   | l reg  | ister1       | ;R0.0 | )   |

|--------|--------|--------|--------------|-------|-----|

| #reg   | uint   | reg    | ister2       | ;RW1  |     |

| #reg   | udir   | nt reg | ister3       | ;RL3  |     |

| #table | e uint | t tab  | = 1, 2, 3, 4 | ;TW0  |     |

| ;      |        |        |              |       |     |

|        | LD     | usint  | register1    | ;LD   | %R0 |

|        | LD     | sint   | register2    | ;LD   | %R1 |

|        | LD     | usint  | register3+3  | ;LD   | %R6 |

|        | LTB    | usint  | tab          | ;LTB  | %T0 |

The variable of the word, uint, int types can be cast to two variables of the byte, uint, int types also by means of the *\_\_\_\_high* and *\_\_\_\_low* prefixes.

| LD | <pre>high (register2)</pre> | ;LD | R2 |

|----|-----------------------------|-----|----|

| LD | <pre>low (register2)</pre>  | ;LD | R1 |

# 4.2.3. Word / uint / int operand

The word, uint and int types data in the scratchpad represent two concrete bytes given by the address of the first of them. The data is saved in such a way that low-significance byte has the low address that the high-significance byte (Intel convention).

The data can assume values of 0 to 65 535 (word, uint) or, when using the highest (upper) bit as the sign, -32768 to +32767 (int).

Figure 4.3 Word, uint, int data saving in the scratchpad WH - higher byte value WL - lower byte value In absolute expression, the address of operand is written in such a way that behind the specifier the W character is written as the symbol of the operand type followed by a numeric value addressing the lower word byte. If, for example, register R14 has the value of \$21 and register R15 a value of \$43, then by means of instruction

LD %RW14

we read a value of \$4321. Similarly, other operands are written.

LD %XW1 WR %YW0 LD %SW53 WR %RW123 LD %DW25 LTB %TW4

Similarly, using the U-operand means working with two physical addresses following each other. For example, if we have a sixteen-input binary unit with address 2 in PLC NS950, the state of the input signals of byte 0 is % 1101 0001 in binary notation and the state of the input signals of byte 1 is %0010 1100 in binary notation, then by means of the following instruction

LD %UW\$9200

we load value \$2CD1.

#### Time unit coding in timer instructions

Timer instructions (TON, TOF, RTO, IMP) work only with the unit type operand containing the current value of the timer. Moreover, it is necessary to enter a time unit, which the instruction should use and in which the value of the timer is measured out. Four time units are possible that are entered by means of a code number 0 to 3 specified in the instruction after the address number. Both items are separated by the full stop. The time units are encoded as follows:

- .0 unit of 10 ms

- .1 unit of 100 ms

- .2 unit of 1 s

- .3 unit of 10 s

If the code of the time unit is not specified, it is understood as zero one, i.e. the unit of 10 ms. Let us specify some examples of timer instructions:

| TON | %RW10.0 | ;timer  | is   | at   | RW10, | unit | of | 10 ms  |

|-----|---------|---------|------|------|-------|------|----|--------|

| TON | %RW10   | ;identi | Lca] | L wi | rite  |      |    |        |

| TOF | %RW24.1 | ;timer  | is   | at   | RW24, | unit | of | 100 ms |

| RTO | %RW32.2 | ;timer  | is   | at   | RW32, | unit | of | 1 s    |

| IMP | %RW34.3 | ;timer  | is   | at   | RW34, | unit | of | 10 s   |

#### Symbolic expression

In symbolic expression, the operand is determined by the *#def*, *#reg*, *#rem*, *#data* and *#table* directives.

|      | input 9 |           | - DMO | romanant |

|------|---------|-----------|-------|----------|

|      |         | register1 | -     | remanent |

| #reg | word    | register2 | ;RW2  |          |

| #reg | uint    | registr3  | ;RW4  |          |

| #reg | int     | registr4  | ;RW6  |          |

#data uint record = 1,2,3,4 ;DW0, DW2, DW4, DW6

#table uint tab = 1,2,3,4 ;TW0

#### Casting to word, uint, int

If we need to cast an operand locally in our user program (we need to use another operand type than it is defined by the above mentioned directives) it is possible to cast it locally by adding the *word*, *uint*, *int* prefixes.

| #reg   | bool    | register1        | ;R0.( | )    |

|--------|---------|------------------|-------|------|

| #reg   | usint   | register2        | ;R1   |      |

| #reg   | udint   | register3        | ;RL2  |      |

| #table | e usint | tab = 1, 2, 3, 4 | ;T0   |      |

| ;      |         |                  |       |      |

| ]      | LD u:   | int register1    | ;LD   | %RW0 |

| 1      | LD in   | nt register2     | ;LD   | %RW1 |

| ]      | LD u:   | int register3+2  | ;LD   | %RW4 |

| ]      | LTB u:  | int tab          | ;LTB  | %TW0 |

#### 4.2.4. Dword / udint / dint operand

The dword, udint and dint types data in the scratchpad represents four concrete bytes determined by the address of the first one of them. The data is saved in such a way that the low-significance byte has the lowest address (Intel convention).

The data assumes values 0 to 4 294 967 295 or, when using the highest (upper) bit as the sign, -2 147 483 648 to +2 147 483 647.

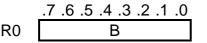

|     |    | .7 .6 .5 .4 .3 .2 .1 .0 |

|-----|----|-------------------------|

| RL0 | R0 | LO                      |

|     | R1 | L1                      |

|     | R2 | L2                      |

|     | R3 | L3                      |

Figure 4.4 Dword, udint, dint data saving in the scratchpad L0 - lowest byte value

In absolute expression, the address of the operand is written in such a way that behind the space specifier the L character is written as the symbol of the operand type followed by a numeric value addressing the lowest byte. If, for example, register R14 has the value of \$21, register R15 the value of \$43, register R16 the value of \$65 and register R17 the value of \$87, then by means of instruction

LD %RL14

we load \$87654321. Similarly, other operands are written.

LD %XL1 WR %YL0 LD %SL53 WR %RL123 LD %DL25 LTB %TL4

The U operand does not enable access in this format.

#### Symbolic expression

In symbolic expression, the operand is determined by the *#def*, *#reg*, *#rem*, *#data* and *#table* directives.

| #def in | put %} | <b>KL4</b>          |                      |

|---------|--------|---------------------|----------------------|

| #rem    | udint  | register1           | ;RL0 remanent        |

| #reg    | dword  | register2           | ;RL4                 |

| #reg    | udint  | registr3            | ;RL8                 |

| #reg    | dint   | registr4            | ;RL12                |

| #data   | udint  | record = 1, 2, 3, 4 | ;DL0, DL4, DL8, DL12 |

| #table  | udint  | tab = 1, 2, 3, 4    | ;TLO                 |

#### Casting to dword, udint, dint

If we need to cast an operand locally in our user program (we need to use another operand type than it is defined by the above mentioned directives) it is possible to cast it locally by adding the *dword*, *udint*, *dint* prefixes.

```

#reg

bool register1

;R0.0

usint register2

#reg

;R1

#req

uint register3

;RW2

#table usint tab = 1,2,3,4

;T0

;

\mathbf{LD}

udint register1

%RL0

:LD

LD

dint register2

;LD

%RL1

LD

udint register3

;LD

%RL2

LTB udint tab

;LTB %TL0

```

#### 4.2.5. Real operand

The real type data in the scratchpad represent four concrete bytes given by the address of the first one of them. The data is saved in such a way that the lowest-significance byte has the lowest address (Intel convention).